- Συγγραφέας Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:45.

- Τελευταία τροποποίηση 2025-01-22 17:21.

VHDL και Verilog θεωρούνται γλώσσες ψηφιακής σχεδίασης γενικής χρήσης, ενώ το SystemVerilog αντιπροσωπεύει την βελτιωμένη έκδοση του Verilog . VHDL έχει ρίζες στο Γλώσσα προγραμματισμού Ada τόσο σε έννοια όσο και σε σύνταξη, ενώ της Verilog Οι ρίζες μπορούν να παρακολουθηθούν σε μια πρώιμη HDL που ονομάζεται Hilo και στη γλώσσα προγραμματισμού C.

Οι άνθρωποι ρωτούν επίσης, ποιο είναι καλύτερο VHDL ή Verilog;

VHDL είναι πιο περίπλοκο από Verilog και το itis έχει επίσης σύνταξη που δεν μοιάζει με C. Με VHDL , έχετε μεγαλύτερες πιθανότητες να γράψετε περισσότερες γραμμές κώδικα. Verilog έχει ένα καλύτερα κατανοεί τη μοντελοποίηση υλικού, αλλά έχει χαμηλότερο επίπεδο δομών προγραμματισμού. Verilog δεν είναι τόσο περίεργο όσο VHDL γι' αυτό είναι πιο συμπαγές.

Επίσης, ποια είναι η χρήση της Verilog; Verilog είναι μια γλώσσα περιγραφής υλικού. κειμενική μορφή για την περιγραφή ηλεκτρονικών κυκλωμάτων και συστημάτων. Εφαρμόζεται στον ηλεκτρονικό σχεδιασμό, Verilog προορίζεται να χρησιμοποιηθεί για επαλήθευση μέσω προσομοίωσης, για ανάλυση χρονισμού, για ανάλυση δοκιμών (ανάλυση δοκιμασιμότητας και ταξινόμηση σφαλμάτων) και για λογική σύνθεση.

Με αυτόν τον τρόπο, ποια είναι η διαφορά μεταξύ Verilog και SystemVerilog;

Το κύριο διαφορά μεταξύ Verilog και SystemVerilog είναι αυτό Verilog είναι μια Γλώσσα Περιγραφής Υλικού, ενώ SystemVerilog είναι μια γλώσσα περιγραφής υλικού και επαλήθευσης υλικού που βασίζεται σε Verilog . Εν συντομία, SystemVerilog είναι μια βελτιωμένη έκδοση του Verilog με επιπλέον χαρακτηριστικά.

Τι είναι το VHDL στο VLSI;

VLSI Σχέδιο - VHDL Εισαγωγή. Διαφημίσεις. VHDL σημαίνει γλώσσα περιγραφής υλικού πολύ υψηλής ταχύτητας ολοκληρωμένου κυκλώματος. Είναι μια γλώσσα προγραμματισμού που χρησιμοποιείται για τη μοντελοποίηση ενός ψηφιακού συστήματος με βάση τη ροή δεδομένων, τη συμπεριφορά και το δομικό στυλ μοντελοποίησης.

Συνιστάται:

Ποια είναι η διαφορά μεταξύ Pebble Tec και Pebble Sheen;

Το Pebble Tec είναι κατασκευασμένο από φυσικά, γυαλισμένα βότσαλα που δημιουργούν μια ανώμαλη υφή και μια αντιολισθητική επιφάνεια. Το Pebble Sheen ενσωματώνει την ίδια τεχνολογία με το Pebble Tec, αλλά χρησιμοποιεί μικρότερα βότσαλα για πιο λείο φινίρισμα

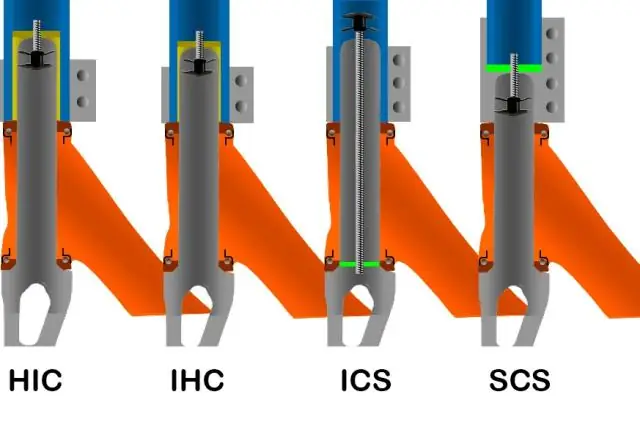

Ποια είναι η διαφορά μεταξύ της συμπίεσης μεταξύ πλαισίου και ενδοπλαισίου;

Η συμπίεση εντός πλαισίου συμβαίνει μόνο σε κάθε πλαίσιο. Η συμπίεση interframe χρησιμοποιεί αυτό το γεγονός για τη συμπίεση κινούμενων εικόνων. Η συμπίεση μεταξύ καρέ περιλαμβάνει την ανάλυση των αλλαγών στην ταινία από καρέ σε καρέ και σημειώνει μόνο τα μέρη της εικόνας που έχουν αλλάξει

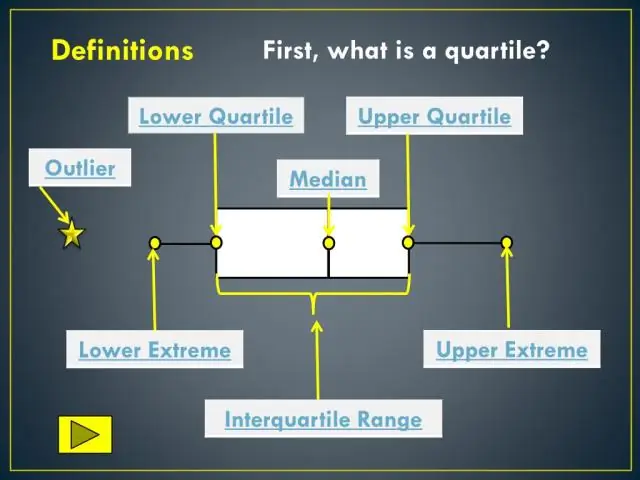

Ποια είναι η διαφορά μεταξύ μιας πλοκής κουτιού και μουστάκι και μιας πλοκής κουτιού;

Μια γραφική παράσταση κουτιού και μουστάκι (μερικές φορές ονομάζεται γραφική παράσταση κουτιού) είναι ένα γράφημα που παρουσιάζει πληροφορίες από μια σύνοψη πέντε αριθμών. Σε διάγραμμα κουτιού και μουστάκι: τα άκρα του κιβωτίου είναι τα άνω και κάτω τεταρτημόρια, επομένως το κουτί εκτείνεται στο εύρος των διατεταρτημορίων. η διάμεσος σημειώνεται με μια κάθετη γραμμή μέσα στο πλαίσιο

Ποια είναι η ομοιότητα και ποια η διαφορά μεταξύ ρελέ και PLC;

Τα ρελέ είναι ηλεκτρομηχανικοί διακόπτες που έχουν πηνίο και δύο τύπους επαφών που είναι NO & NC. Αλλά ένας προγραμματιζόμενος λογικός ελεγκτής, το PLC είναι ένας μίνι υπολογιστής που μπορεί να λάβει αποφάσεις με βάση το πρόγραμμα και την είσοδο και την έξοδο του

Ποια είναι η διαφορά μεταξύ είναι και όπως στο C#;

Η διαφορά μεταξύ των τελεστών is και as είναι η εξής: Ο τελεστής is χρησιμοποιείται για να ελέγξει εάν ο τύπος χρόνου εκτέλεσης ενός αντικειμένου είναι συμβατός με τον συγκεκριμένο τύπο ή όχι, ενώ ως τελεστής χρησιμοποιείται για την εκτέλεση μετατροπής μεταξύ συμβατών τύπων αναφοράς ή τύπων Nullable